英语原文共 7 页,剩余内容已隐藏,支付完成后下载完整资料

用于仪表和控制的具有CAN,RS-232,以太网和AXI GPIO的Zynqreg;SoC通用接口

Abhijeet Kumar , Rachana Rajpal, Harshad Pujara, 亚太区首席技术官Matt分区,Praveenalal Edappala

等离子体研究学院,甘地,印度古吉拉特邦

要点:

bull;我们在Zynqreg;SoC上设计了通用接口,CAN,RS-232,以太网和AXI GPIO用于仪表和控制。 该项目基于Zynqreg;-7000系列xc7z020clg484-1芯片。

bull;我们探索了从Vivado的硬件开发到SDK中使用C语言开发的软件开发的完整设计流程,然后连接了LabVIEW开发的主机应用程序。

bull;我们还探讨了如何在Vivado中使用AXI总线接口进行定制IP。

bull;对于那些想在Zynqreg;SoC上制作定制硬件的用户很有用。

文章信息:

文章历史:

收到2015年6月19日

收到修订形式2016年5月2日2016年6月13日接受

在线可用2016年7月2日

关键词:Zynq、CAN、以太网、AXI-GPIO、自定义IP、UART

摘要:

本文介绍了在最新的Zynqreg;-7000全可编程SoC(AP SoC)[1]器件上开发的应用程序,它将基于ARMreg;处理器的可编程性与FPGA的硬件可编程性集成在单个器件上。在本文中,我们实现了使用CAN,RS-232,以太网和AXI GPIO等各种接口的应用程序,使得在LabVIEW中运行在PC上的主机应用程序可以与任何至少有一个可用接口的硬件进行通信。Zynq-7000所有可编程SoC(片上系统)将可定制智能注入今天的嵌入式系统,以满足您独特的应用需求。这个FPGA系列适用于高端应用,因为它在单芯片上具有巨大的资源。它为您提供自己的定制硬件IP,实际上我们已经在我们的设计中将我们的定制IP称为my IP。这款芯片的优点在于它可以为您的定制IP编写驱动程序,该IP已连接AXI总线层。将硬件信息导出到软件开发工具包(SDK)后,该工具能够为自定义IP编写驱动程序。这在很大程度上简化了您的开发。在某种程度上,该应用程序为用户提供了通用接

口选项。用户还可以通过LabVIEW测试应用程序GUI将数字数据写入GPIO(通用输入输出)。该项目可用于远程控制,并通过以太网或CAN网络监控数据。

copy;2016 Elsevier B.V.保留所有权利

A. Kumar et al. / Fusion Engineering and Design 112 (2016) 865–871

一、介绍

有许多前端电子和信号调理单元用于SST-1和ADITYA tokamak的各种诊断。这些诊断电子设备具有不同类型的握手,包括RS-232,CAN总线和以太网等。因此,需要可以在一个地方远程控制这些参数的系统。为了实现这一要求,zc702开发板[7]被选为原型能够远程控制放大器增益,滤波频率等参数的控制系统,并将采集的数据发送到服务器,客户端可以随时查看这些数据进行分析。

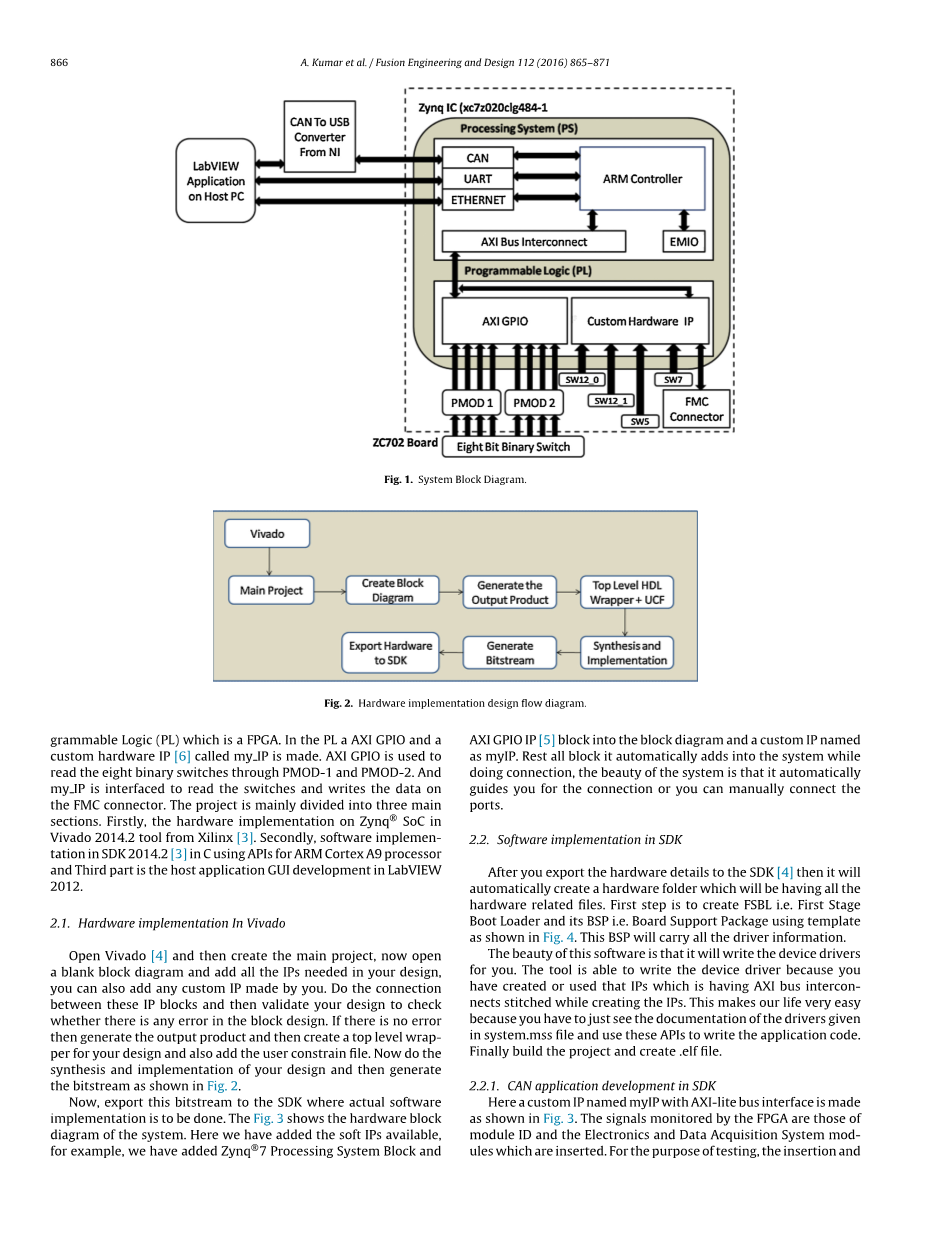

二、系统框图

如图1所示,zc-702板[7]由虚线表示,它由许多接口组成,但我仅突出了我在设计中使用的那些接口。因此,它有两个PMOD连接器,一些开关,FMC连接器和Zynqreg;IC(xc7z020clg484-1)。该IC主要分为处理系统(PS)和Pro-可编程逻辑(PL)是FPGA。在PL中,AXI GPIO和自定义硬件IP [6]称为IP。AXI GPIO用于通过PMOD-1和PMOD-2读取八个二进制开关。并且我的IP接口读取交换机并将数据写入FMC连接器。该项目主要分为三个主要部分。首先,Xilinx的Vivado 2014.2工具中Zynqreg;SoC的硬件实现[3]。其次,使用ARM Cortex A9处理器的API中的SDK 2014.2 [3]中的软件实现,第三部分是LabVIEW 2012中的主机应用程序GUI开发。

图1:系统框图

A. Kumar et al. / Fusion Engineering and Design 112 (2016) 865–871

图2:硬件实现设计流程图

2.1Vivado中硬件的实现

打开Vivado [4]然后创建主项目,现在打开一个空白的框图,并添加您设计中所需的所有IP,还可以添加您所创建的任何自定义IP。执行这些IP块之间的连接,然后验证您的设计,以检查块设计中是否有任何错误。如果没有错误,则生成输出产品,然后为您的设计创建顶级包装,并添加用户约束文件。如图2所示,做设计的合成和实现,然后生成比特流。

现在,将此比特流导出到要实现实际软件实现的SDK。如图3所示,显示了系统的硬件框图。这里我们添加了可用的IP,例如,我们在框图和自定义IP--myIP中添加了Zynqreg;7处理系统块和AXI GPIO IP [5]块。在进行连接时,其余全部块会自动添加到系统中,系统的优点是它自动引导您进行连接,或者您可以手动连接端口。

图3:创建于Vivado的赫尔德瓦尔框图

A. Kumar et al. / Fusion Engineering and Design 112 (2016) 865–871

图4:软件实现设计流程图

2.2 SDK中的软件实现

将硬件详细信息导出到SDK [4]之后,它将自动创建一个将具有所有硬件相关文件的硬件文件夹。第一步骤是创建FSBL即第一阶段引导加载器和它的GNP即板级支持包使用模板,如图4所示。该BSP将携带所有的驱动程序信息。这个软件的优点是它会为您编写设备驱动程序。该工具能够编写设备驱动程序,因为您创建或使用了在创建IP时具有AXI总线连接的IP。这使我们的生活非常简单,因为您只要看到system.mss文件中给出的驱动程序的文档,并使用这些API来编写应用程序代码,最后构建项目并创建.elf文件。

2.2.1 CAN应用程序开发SDK

这里有一个使用AXI-Lite总线接口命名为myIP的定制IP,如图3所示。由FPGA监控的信号是插入的模块ID和电子数据采集系统模块的信号。为了测试,模块的插入和删除是通过使用板上可用的开关来模拟的。控制信号由硬件产生,要设置的参数值在FMC连接器上输出。

如图5的流程图所示,最初,程序重置控制器,然后它检查控制器是否处于配置模式。当进入配置模式时,它将CAN选通引脚设置为LOW,并设置波特率。现在它变为正常模式,在这种模式下,硬件可以同时读写CAN数据包。然后检查控制器是否进入正常模式,如果是,则可以并行地接收和发送数据包。在发送CAN数据包时,检查TX FIFO是否满,如果否,则发送数据并检查是否设置了Tx OK标志,表示事务已完成。而在接收到CAN数据包的同时,它检查Rx OK标志,如果该标志被设置,则意味着已经接收到CAN数据包。然后它读取数据并清除标志,以便它可以接收下一个CAN [2]数据包(如果可用)。

- Kumar et al. / Fusion Engineering and Design 112 (2016) 865–871

图5:CAN应用编程流程

2.2.2 以太网与SDK中的GPIO应用程序开发

在这个应用中,我们通过AXI GPIO读取8位二进制开关数据,如系统框图1所示。开关连接到板上的PMOD1和PMOD2连接器。数据流从八位二进制交换机→PMOD1和PMOD2→AXI GPIO→AXI总线互连→ARM控制器→以太网外设→LabVIEW主机应用→以太网外设→ARM控制器。主机应用程序每隔一秒钟读取数据,然后将其显示在波形图中。将来可以将其连接到ADC以获取某些MHz范围内的数据。

如图6的流程图所示,首先,程序初始化AXI GPIO和以太网驱动程序。然后,它将AXI GPIO [2]的方向设置为输入,以便它可以读取二进制开关。此外,它创建一个新的TCP结构,绑定到指定的端口,监听连接,最后为传入连接使用回调。一旦完成,它将检查任何客户端正在请求数据,如果是,则它开始读取八位二进制开关数据。然后检查任何客户端请求数据,如果是,那么它开始读取八位二进制开关数据。然后它将接收的数据传输到以太网发送缓冲区,并检查TCP发送缓冲区是否为空。如果是,则表示已发送数据,然后终止程序。

A. Kumar et al. / Fusion Engineering and Design 112 (2016) 865–871

图6:以太网与AXI GPIO应用程序流程图

图7:以太网应用编程流程图

2.2.3 SDK中的以太网应用开发

在这个以太网[2]应用中,我们在SDK中的数组中生成400字节的数据,然后通过用户通过LabVIEW主机应用程序请求数据时,通过Eth-ernet API发送此数

据。

A. Kumar et al. / Fusion Engineering and Design 112 (2016) 865–871

如图7的流程图所示。首先程序初始化以太网驱动程序,然后它创建一个新的TCP结构,绑定到指定的端口,监听连接,最后为传入连接使用回调。一旦这样做,它检查任何客户端正在请求数据,如果是,则将400字节的数据包发送到TCP发送缓冲区,并检查TCP发送缓冲区是否为空。如果是,则表示已发送数据,然后它终止程序。

2.2.4 UART应用程序开发在SDK中

在UART [2]应用程序中,我们通过UART端口读取数据,然后通过UART API向接收到的数据添加2,发送数据。如下图8所示为SDK中的软件应用程序代码开发流程图。

首先程序初始化UART驱动程序,然后将UART配置为NORMAL模式,然后在设置波特率和数据格式后,检查任何接收到的数据接收缓冲区中的字节。然后程序向接收的数据字节添加两个字节并将其发送回Tx缓冲区。然后它检查Tx缓冲区为空,如果是,则表示数据字节已被传输。

图8 :UART或RS232应用编程流程图

2.3 在LabVIEW中主机应用开发

一个集成的主机应用程序在它给出的LABVIEW中用户可以从CAN,以太网接口任何一个协议一次使用AXI GPIO,以太网和UART(RS232)。在CAN应用中,用户可以读写不同的参数,如GAIN,滤波器等也可以随时读取CAN数据包被插入到系统中。在使用AXI GPIO应用的以太网中,用户可以通过读取八位二

A. Kumar et al. / Fusion Engineering and Design 112 (2016) 865–871

进制开关AXI GPIO IP,它以每隔一秒的间隔读取开关将读取的数据绘制到图形中。以太网应用用户可以请求服务器发送数据,服务器发送400字节数据包通过以太网回到主机,最后在RS232应用用户可以向zc702板发送任何数据系统在将两个数据添加到接收到的数据后返回数据返回主机应用程序,如结果所示。

3.结果

如图9 所示,CAN应用程序GUI正在读取CAN数据包,如果任何新模块插入系统或从系统中删除。此应用程序还可以设置像GAIN,Filters等参数。对于特定模块的特定通道。这个应用程序在停止应用程序后,还将数据记录为.xls文件格式。

图9.基于LabVIEW 的CAN应用程序GUI

图10显示了使用AXI GPIO的以太网快照LabVIEW中的应用程序GUI。在这个应用中用户可以设置IP以太网的地址和端口地址开始读取八个来自PMOD1的数位GPIO(通用输入输出)数据zc702板的PMOD2每隔一秒钟绘制一次读取的数据图表。

A. Kumar et al. / Fusion Engineering and Design 112 (2016) 865–871

图10.基于 LabVIEW的以太网AXI GPIO应用GUI

图11显示了LabVIEW中用户的以太网应用GUI可以设置以太网的IP地址和端口地址并进行请求服务器发送数据和服务器发送400字节的数据包通过以太网回到主机。我们可以读取400字节数据包上单击就可以看出这个应用可以用于制作高速数据采集系统。

图11:基于LabVIEW的以太网应用GUI

图12显示了LabVIEW中的UART应用程序GUI这个应用程序我们通过UART和ARM发送一些数据控制器通过UART读取数据并进行修改通过将两个接收到的数据添加回主机来接收数据。这只是确认数据已被ARM控制器读取而不是返

A. Kumar et al. / Fusion Engineering and Design 112 (2016) 865–871

回本地的UART发回模式。

图12:基于LabVIEW的应用UART GUI

4.结论

Vivado设计套件,是FPGA厂商赛灵思公司2012年发布的集成设计环境。包括高度集成的设计环境和新一代从系统到IC级的工具,这些均建立在共享的可扩展数据模型和通用调试环境基础上。集成的设计环境--Vivado设计套件包括高度集成的设计环

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[140167],资料为PDF文档或Word文档,PDF文档可免费转换为Word